## BASIC ARM INSTRUCTIONS

- Instructions include various "fields" that encode combinations of

Opcodes and arguments

- special fields enable extended functions (more in a minute)

- several 4-bit OPERAND fields, for specifying the sources and destination of the operation, usually one of the 16 registers

- Embedded constants ("immediate" values) of various sizes,

The "basic" data-processing instruction formats:

|         | 4    | 3   | 4      | 1 | 4  | 4  | 8       | 4   |

|---------|------|-----|--------|---|----|----|---------|-----|

| R type: | 1110 | 000 | Opcode | 0 | Rn | Rd | 0000000 | Rm  |

|         | 4    | 3   | 4      | 1 | 4  | 4  | 4       | 8   |

| I type: | 1110 | 001 | Opcode | 0 | Rn | Rd | Shift   | lmm |

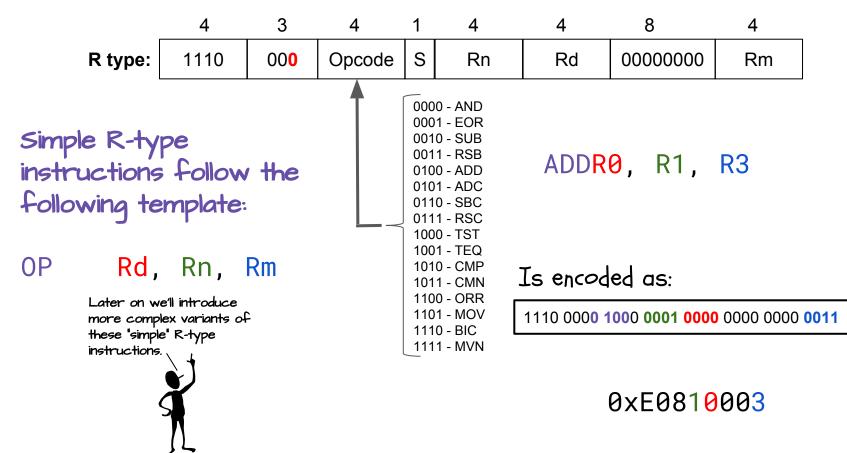

## R-TYPE DATA PROCESSING

Instructions that process three-register arguments:

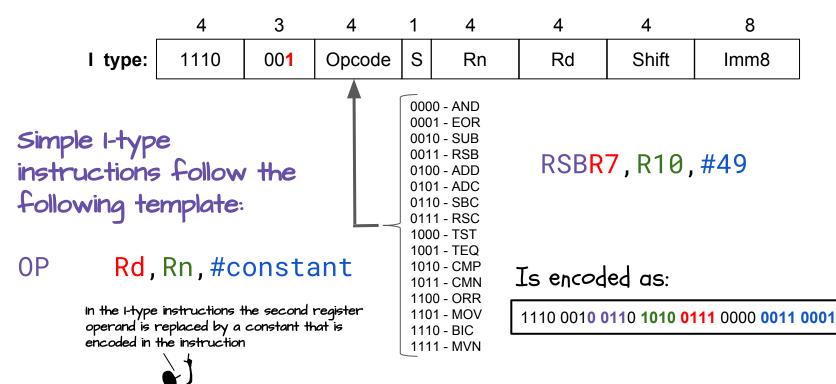

#### I-TYPE DATA PROCESSING

Instructions that process two registers and a constant:

#### 0xE26A7031

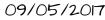

#### I-TYPE CONSTANTS

ARM7 provides only 8-bits for specifying an immediate constant value. Given that ARM7 is a 32-bit architecture, this may appear to be a severe limitation. However, by allowing for a shift (actually a "*right rotation*") to be applied to the constant.

imm32 = (imm8 >> (2 \* shift)) | (imm8 << (32 - (2 \* shift)))</pre>

Example: 1920 is encoded as:

ShiftImm81101

$$00011110$$

=  $(30 >> (2*13)) | (30 << (32 - (2*13)))$ =0|=0|=1920

How would 256 be encoded? Shift

| Shift | lmm8     |

|-------|----------|

| 1100  | 00000001 |

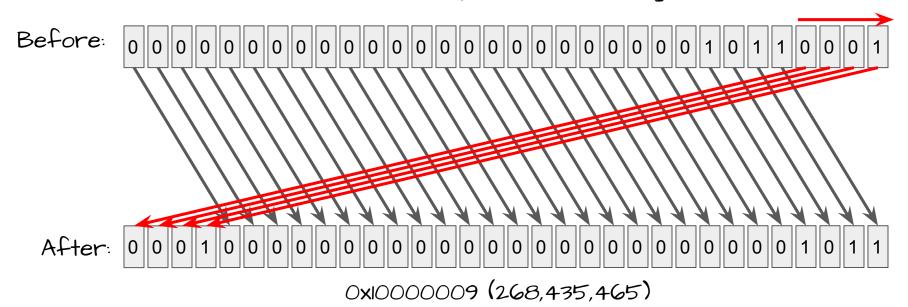

## Illustrating a right rotation

The "shift" field of the 1-type instruction is a misnomer. It is acually a "rotate-right". What's a rotate right?

OxBI (209) rotated 4 postions to the right

## ARM IMMEDIATE CONSTANTS

8

Recall that immediate constants are encoded in two parts: Some constants can be encoded in multiple ways.

Thus fewer than 4096 32-bit numbers can be represented.

There are actually only **3073** distinct constants. There are 16, "Os" and 4 ways to represent all powers 2. How might you encode 256?

| 1100 | 00000001 | 1101 | 00000100 |

|------|----------|------|----------|

| 1110 | 00010000 | 1111 | 01000000 |

|      |          |      |          |

## READ THE INSTRUCTIONS

#### .. when all else fails

- What do instructions do?

- How are instructions decoded?

- Uniformity and Symmetry

- Cramming stuff in

- CPU state

- Condition codes

- Program Status Register (PSR)

#### A CLOSER LOOK AT THE OPCODES

The Opcode field is common to both of the basic instruction types

|                                                                                                                      | 4    | 3   | 4      | 1                                                                                       | 4                                                                                                                                                                            | 4     | 8                                                                                                                                                    | 4                                                                                                                                                                          | _                                                                                              |

|----------------------------------------------------------------------------------------------------------------------|------|-----|--------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| R type:                                                                                                              | 1110 | 000 | Opcode | S                                                                                       | Rn                                                                                                                                                                           | Rd    | 00000000                                                                                                                                             | Rm                                                                                                                                                                         |                                                                                                |

| I type:                                                                                                              | 1110 | 001 | Opcode | s                                                                                       | Rn                                                                                                                                                                           | Rd    | Rotate                                                                                                                                               | lmm8                                                                                                                                                                       |                                                                                                |

| ARM data proce<br>instructions can<br>four basic grou<br>• Arithmetic<br>• Logic (4)<br>• Compariso<br>• Register to | be   |     | Comp 4 | 000<br>001<br>001<br>010<br>010<br>011<br>100<br>100<br>101<br>110<br>110<br>111<br>111 | 0 - AND<br>1 - EOR<br>0 - SUB<br>1 - RSB<br>0 - ADD<br>1 - ADC<br>0 - SBC<br>1 - RSC<br>0 - TST<br>1 - TEQ<br>0 - CMP<br>1 - CMN<br>0 - ORR<br>1 - MOV<br>0 - BIC<br>1 - MVN | If se | t, it tells the<br>tain some 's<br>instructio<br>This<br>f<br>f<br>f<br>f<br>f<br>f<br>f<br>f<br>f<br>f<br>f<br>f<br>f<br>f<br>f<br>f<br>f<br>f<br>f | the "S" field<br>e processo<br>state" after<br>in has execu<br>"state" is in<br>orm of 5-f<br>Many ins<br>(all we've<br>far) have<br>sets the st<br>iants the op<br>an "S" | or to<br>the<br>uted.<br>Tags.<br>Hags.<br>structions<br>seen thus<br>a special<br>tate flags. |

## ARITHMETIC INSTRUCTIONS

ADD R3, R2, R12

SUB R0, R4, R6

RSB R0, R4, R2

ADC R1, R5, R8

SBC R2, R5, R7

RSC R1, R5, R3

$R3 \leftarrow R2 + R12$

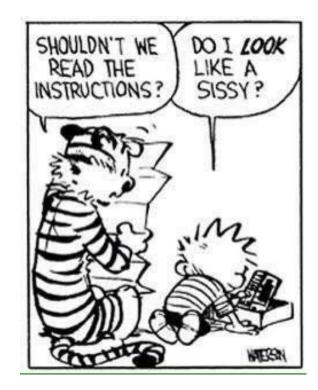

Registers can contain either 32-bit unsigned values or 32-bit 2's-complement signed values.

- R0  $\leftarrow$  R4 - R6 Once more, either 32-bit unsigned values or 32-bit 2's-complement signed values.

r R0  $\leftarrow$  - R4 + R2

The operands of the subtraction are in reversed order. It is called "Reverse Subtract". Why? The I-type version makes more sense.

Where "C" is the Carry-out from some earlier instruction (usually an ADDS or ADCS) as saved in the Program Status Register (PSR)

$R2 \leftarrow R5 - R7 - 1 + C$ Where "C" is the Carry-out from some earlier instruction (usually a SUBS or SUBCS) as saved in the PSR

$RI \leftarrow -R5 + R3 - I + C$

$RI \leftarrow R5 + R8 + C$

"Reverse Subtract" with a Carry. Usually a carry generated from a previous RSBS or RSCS instruction.

## LOGIC INSTRUCTIONS

Logical operations on words operate "bitwise", that is they are applied to corresponding 0000 0000 0000 0000 1111 1111 0000 0000 **R1**: bits of both source operands. 0000 0000 0000 0000 1111 0000 1111 0000 R2: 0000 0000 0000 0000 1111 0000 0000 0000 AND R0, R1, R2 **R0**: 0000 0000 0000 0000 1111 1111 1111 0000 **R0**: ORR R0, R1, R2 EOR R0, R1, R2 Commonly called "exclusive-or" 0000 0000 0000 0000 0000 1111 **R0**: 1111 0000 BIC R0, R1, R2 Called "Bit-clear" R0:  $R0 \leftarrow RI \& (R2)$ 0000 0000 0000 0000 0000 1111 0000 0000

## STATUS FLAGS

Now it is time to discuss what status flags are available. These five status flags are kept in a special register called the Program Status Register (PSR). The PSR also contains other important bits that control the processor.

- N set if the result of an opeartion is negative (Most Significant Bit (MSB) is a 1)

- Z set if the result of an operation is "O"

- C set if the result of an operation has a carry out of it's MSB

- V set if a sum of two positive operands gives a negative result, or if the sum of two negative operands gives a positive result

- Q a sticky version of overflow created by instructions that generate multiple results (more on this later on).

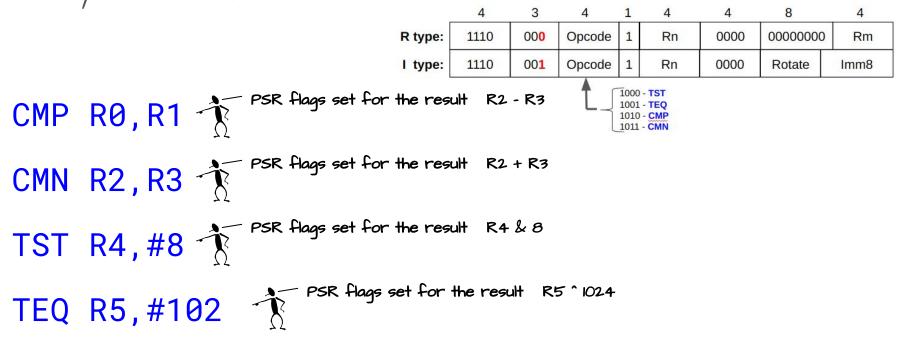

## COMPARISON INSTRUCTIONS

These instructions modify the status flags, but leave the contents of the registers unchanged. They are used to test register contents, and they **must** have their "S" bit set to "I". They also don't modify their Rd, and by **convention**, Rd is set to "0000".

#### REGISTER TRANSFER

These instructions are used to transfer the contents of one register to another, or simply to initialize the contents of a register. They make use of only one operand, and, by convention, have their Rn field set to "0000".

MOV R0, R3  $rac{1}{100}$   $rac{1}{100}$  rac

|                          | 4    | 3   | 4      | 1 | 4    | 4  | 8        | 4    |  |  |  |

|--------------------------|------|-----|--------|---|------|----|----------|------|--|--|--|

| type:                    | 1110 | 000 | Opcode | S | 0000 | Rd | 00000000 | Rm   |  |  |  |

| type:                    | 1110 | 001 | Opcode | s | 0000 | Rd | Rotate   | Imm8 |  |  |  |

| 1101 - MOV<br>1111 - MVN |      |     |        |   |      |    |          |      |  |  |  |

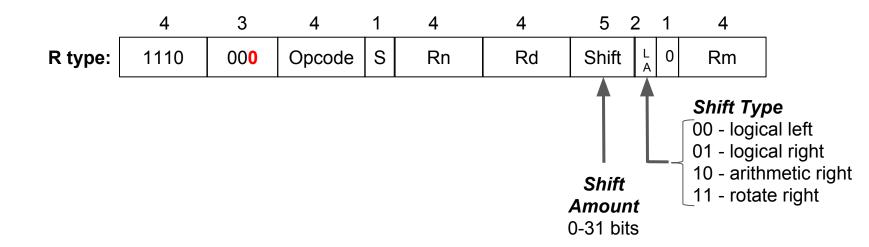

## ARM SHIFT OPERATIONS

A novel feature of ARM is that **all** data-processing instructions can include an optional "shift", whereas most other architectures have separate shift instructions. This is actually very useful as we will see later on. The key to shifting is that 8-bit field between Rd and Rm.

#### 09/05/2017

Left Shifts effectively multiply the contents of a register by 2° where s is the shift amount.

#### MOV R0, R0, LSL #7

LEFT SHIFTS

| RØ | before: | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0111 | = 7                        |

|----|---------|------|------|------|------|------|------|------|------|----------------------------|

| R1 | after:  | 0000 | 0000 | 0000 | 0000 | 0000 | 0011 | 1000 | 0000 | = 7 * 2 <sup>7</sup> = 896 |

Shifts can also be applied to the second operand of any data processing instruction

ADD R1, R1, R0, LSL #7

## RIGHT SHIFTS

Right Shifts behave like *dividing* the contents of a register by 2<sup>s</sup> where s is the shift amount, *if* you assume the contents of the register are *unsigned*.

#### MOV R0, R0, LSR 2

| R0 b | efore: | 0000              | 0000 | 0000 | 0000 | 0000 | 0100 | 0000 | 0000 | = 1024                        |

|------|--------|-------------------|------|------|------|------|------|------|------|-------------------------------|

| R1   | after: | <mark>0000</mark> | 0000 | 0000 | 0000 | 0000 | 0001 | 0000 | 0000 | = 1024 / 2 <sup>2</sup> = 256 |

## ARITHMETIC RIGHT SHIFTS

Arithmetic right Shifts behave like *dividing* the contents of a register by 2<sup>s</sup> where s is the shift amount, *if* you assume the contents of the register are *signed*.

#### MOV R0, R0, ASR #2

| R0 before: | 1111 1111               | 1111 1111 | 1111 1100 | 0000 0000 | = -1024                         |

|------------|-------------------------|-----------|-----------|-----------|---------------------------------|

| R1 after:  | <mark>11</mark> 11 1111 | 1111 1111 | 1111 1111 | 0000 0000 | = -1024 / 2 <sup>2</sup> = -256 |

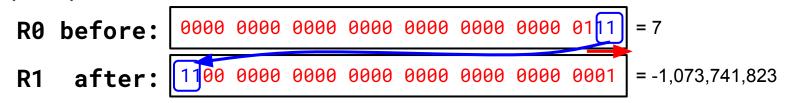

# ROTATE RIGHT SHIFTS

Rotating shifts have no arithmetic analogy. However, they don't lose bits like both logical and arithmetic shifts. We saw rotate right shift used for the I-type "immediate" value earlier.

#### MOV R0, R0, ROR #2

Why no rotate left shift?

- Ran out of encodings?

- Almost anything Rotate lefts can do ROR can do as well!

#### NEXT TIME

Instructions still missing

- Access to memory

- Branches and Calls

- Control

- Multiplication?

- Division?

- Floating point?