# Synchronous Logic

- 1) Sequential Logic

- 2) Synchronous Design

- 3) Synchronous Timing Analysis

- 4) Single Clock Design

- 5) Finite State Machines

- 6) Turing Machines

- 7) What it means to be "Computable"

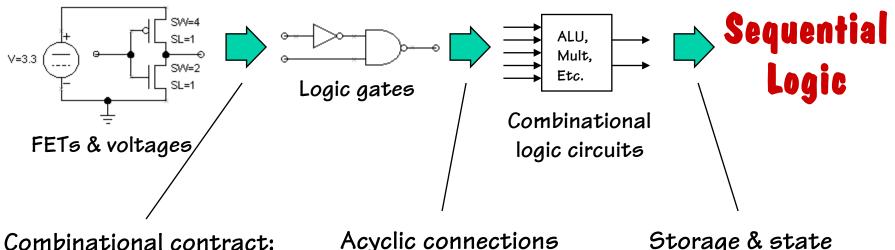

## Road Traveled So Far...

- Voltage-based "bits"

- 1-bit per wire

- Generate quality outputs, tolerate inferior inputs

- Combinational contract

- Complete in/out/timing spec

Acyclic connections Composable blocks Design:

- truth tables

- sum-of-products

- muxes

- ROMs

Storage & state Dynamic discipline Finite-state machines Throughput & latency Pipelining

Our motto: Sweat the details once, and then put a box around it!

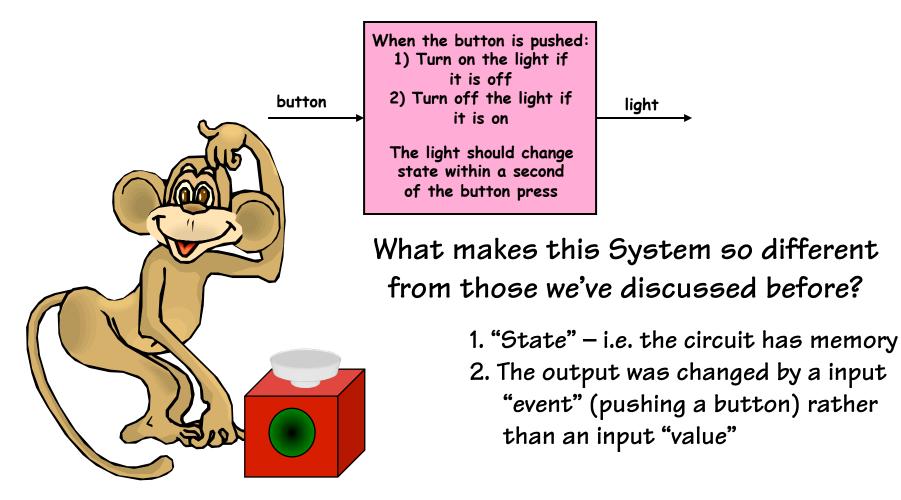

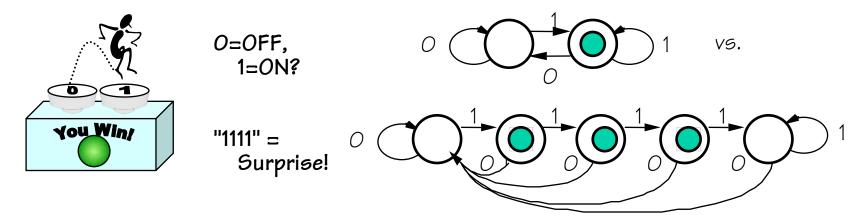

# Something We Can't Build (Yet)

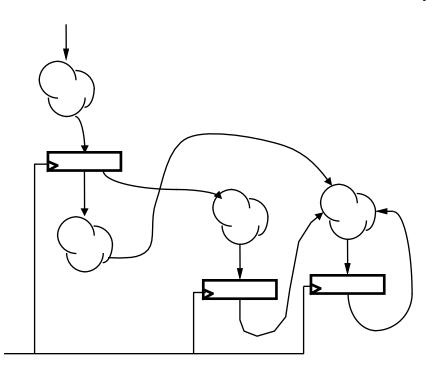

What if you were given the following system design specification?

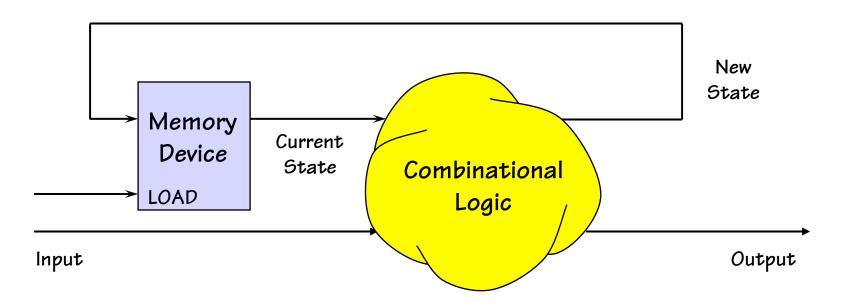

# "Sequential" = Stateful

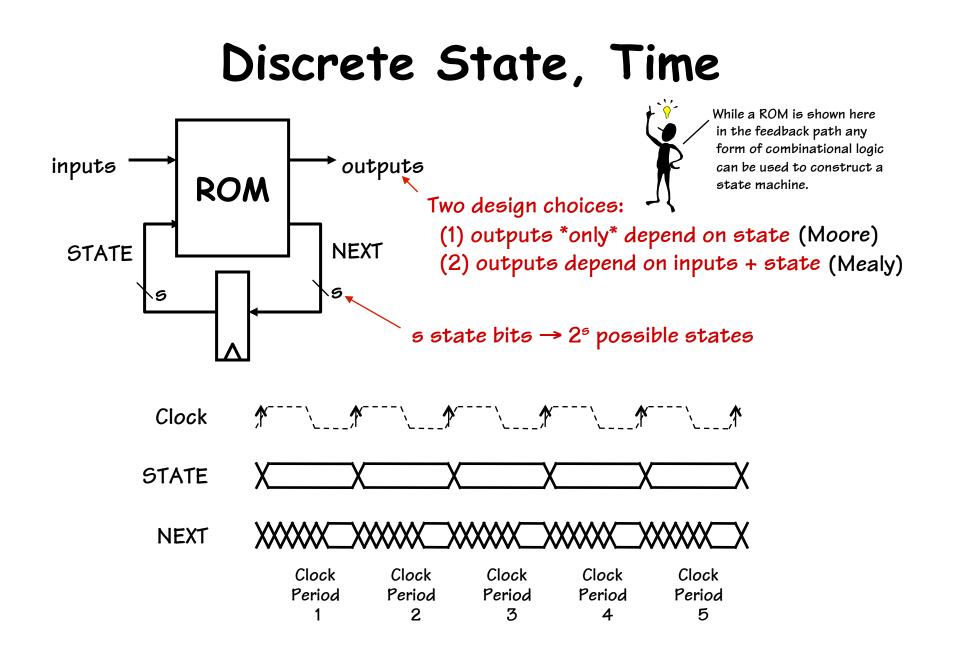

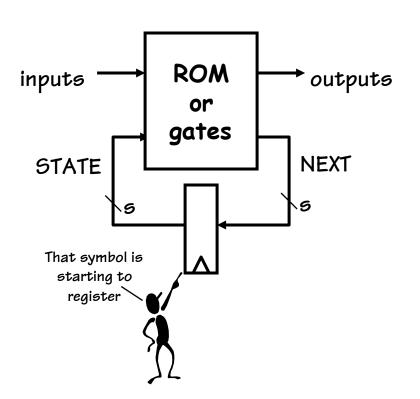

Plan: Build a Sequential Circuit with stored digital STATE -

- MEMORY stores CURRENT state

- Combinational Logic computes

- the NEXT state (Based on inputs & current state)

- the OUTPUTs (Based on inputs and/or current state)

- State changes on LOAD control input

Didn't we develop some memory devices last time?

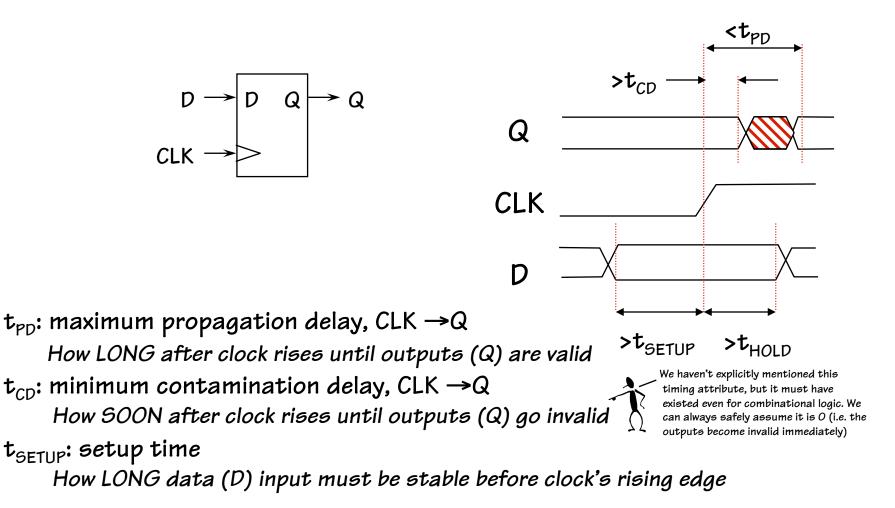

# **Review of Flip Flop Timing**

t<sub>HOLD</sub>: hold time

How LONG data (D) inputs must be held after clock's rising edge

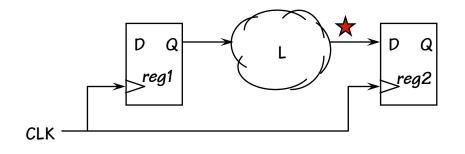

# "Synchronous" Timing Analysis

- $\mathbf{t}_{1} = \mathbf{t}_{\text{CD,reg1}} + \mathbf{t}_{\text{CD,L}} \geq \mathbf{t}_{\text{HOLD,reg2}}$

- $t_2 = t_{\text{PD,reg1}} + t_{\text{PD,L}} \leq t_{\text{CLK}} t_{\text{SETUP,reg2}}$

Questions for register-based designs:

- How much time for useful work (i.e. for combinational logic delay)?

- Does it help to guarantee a minimum t<sub>CD</sub>? How 'bout designing registers so that

$\mathbf{t}_{\text{CD,reg}} \geq \mathbf{t}_{\text{HOLD,reg}}?$

What happens if CLK signal doesn't arrive at the two registers at exactly the same time (a phenomenon known as "clock skew")?

Minimum Clock Period :

$$t_{CLK} \ge t_{PD,reg1} + t_{PD,L} + t_{SETUP,reg2}$$

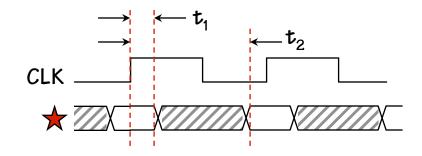

# Example: Flip Flop Timing

#### Questions:

1. t<sub>CD</sub> for the ROM?

$t_{CD,REG} + t_{CD,ROM} > t_{H,REG}$   $1 \text{ ns } + t_{CD,ROM} > 2 \text{ nS}$   $t_{CD,ROM} > 1 \text{ nS}$

#### 2. Min. clock period?

$t_{CLK} > t_{PD,REG} + t_{PD,ROM} + t_{S,REG}$  $t_{CLK} > 3 \text{ ns} + 5 \text{ ns} + 2 \text{ nS}$  $t_{CLK} > 10 \text{ nS}$

#### 3. Constraints on inputs?

"start", "O", and "1" must be valid  $t_{PD,ROM} + t_{S,REG} = 5 + 2 = 7 \text{ ns}$ before the clock and held  $t_{H,REG} - t_{CD,ROM} = 2 - 1 = 1 \text{ ns}$ after it.

# Single Synchronous Clock Design

Sequential ≠ Synchronous

However, Synchronous = A recipe for robust sequential circuits:

- No combinational cycles (other than those already built into the registers)

- Only cares about values of combinational circuits just before rising edge of clock

- Clock period greater than every combinational delay

- Changes state after all logic transitions have stopped!

# Designing Sequential Logic

Sequential logic is used when the solution to some design problem involves a *sequence* of steps:

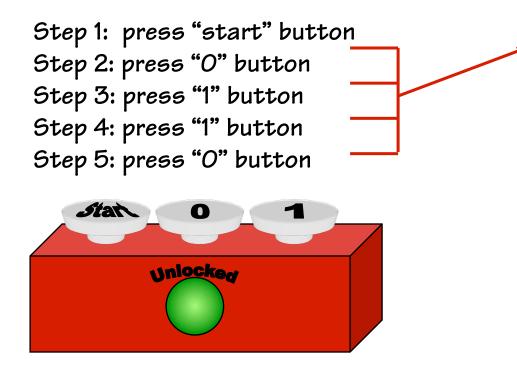

How to open digital combination lock w/ 3 buttons ("start", "O" and "1"):

Information remembered between steps is called state. Might be just what step we're on, or might include results from earlier steps we'll need to complete a later step.

# Implementing a "State Machine"

|                                                  | Current state  |             | "start" | "1" | <i>"O"</i> | Next st | ate         | unlock |

|--------------------------------------------------|----------------|-------------|---------|-----|------------|---------|-------------|--------|

|                                                  |                |             | 1       |     |            | start   | 000         | 0      |

| This is<br>starting to<br>look like a<br>PROGRAM | start          | 000         | 0       | 0   | 1          | digit1  | 001         | 0      |

|                                                  | start          | 000         | 0       | 1   | 0          | error   | 101         | 0      |

|                                                  | start          | 000         | 0       | 0   | 0          | start   | 000         | 0      |

|                                                  | digit1         | 001         | 0       | 1   | 0          | digit2  | 010         | 0      |

|                                                  | digit1         | 001         | 0       | 0   | 1          | error   | 101         | 0      |

|                                                  | digit1         | 001         | 0       | 0   | 0          | digit1  | 001         | 0      |

|                                                  | digit2         | 010         | 0       | 1   | 0          | digit3  | <i>O</i> 11 | 0      |

|                                                  | <br>digit3<br> | <i>O</i> 11 | 0       | 0   | 1          | unlock  | 100         | 0      |

|                                                  | unlock         | 100         | 0       | 1   | 0          | error   | 101         | 1      |

|                                                  | unlock         | 100         | 0       | 0   | 1          | error   | 101         | 1      |

|                                                  | unlock         | 100         | 0       | 0   | 0          | unlock  | 100         | 1      |

|                                                  | error          | 101         | 0       |     |            | error   | 101         | 0      |

This flavor of "truth-table" is called a "state transition table"

6 different states  $\rightarrow$  encode using 3 bits

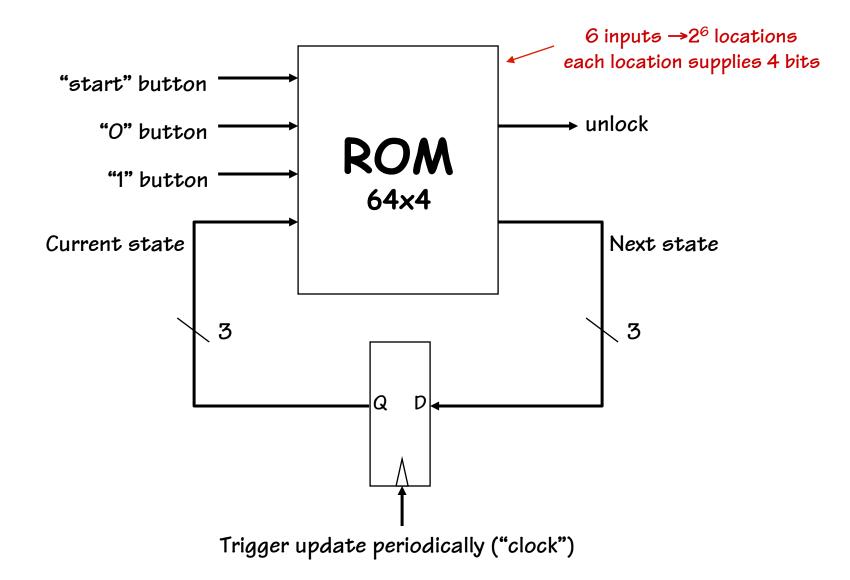

## Now Do It With Hardware!

### Abstraction du jour: Finite State Machines

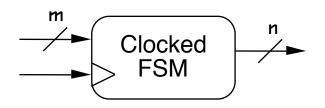

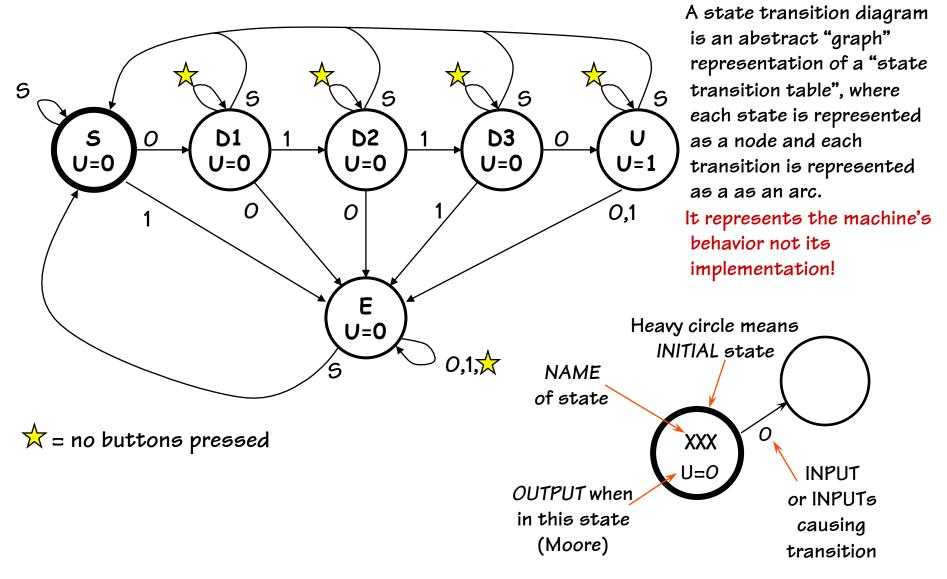

#### A FINITE STATE MACHINE has

- k STATES  $S_1 \dots S_k$  (one is "initial" state)

- m INPUTS  $I_1 \dots I_m$

- n OUTPUTS  $O_1 \dots O_n$

- Transition Rules S'(S,i) for each state S and input i

- Output Rules Out(S) for each state S

### State Transition Diagrams

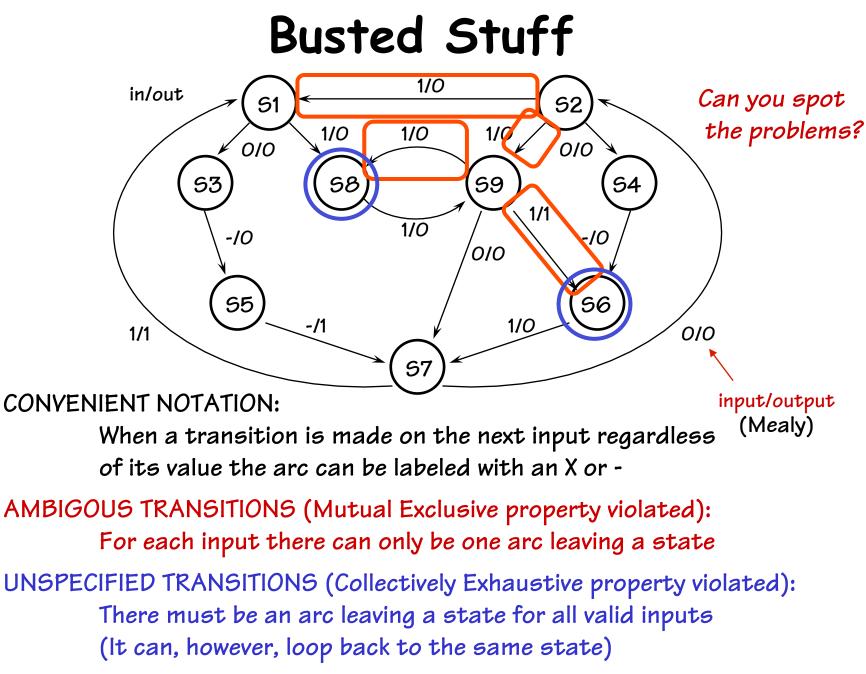

## Valid State Diagrams

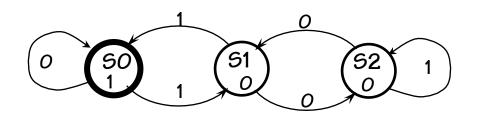

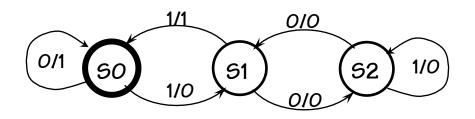

MOORE Machine: Outputs on States

MEALY Machine: Outputs on Transitions

Arcs leaving a state must be:

(1) mutually exclusive

can only have one choice for any given input value

(2) collectively exhaustive

every state must specify what happens for each possible input combination. "Nothing happens" means arc back to itself.

### Let's Play State Machine

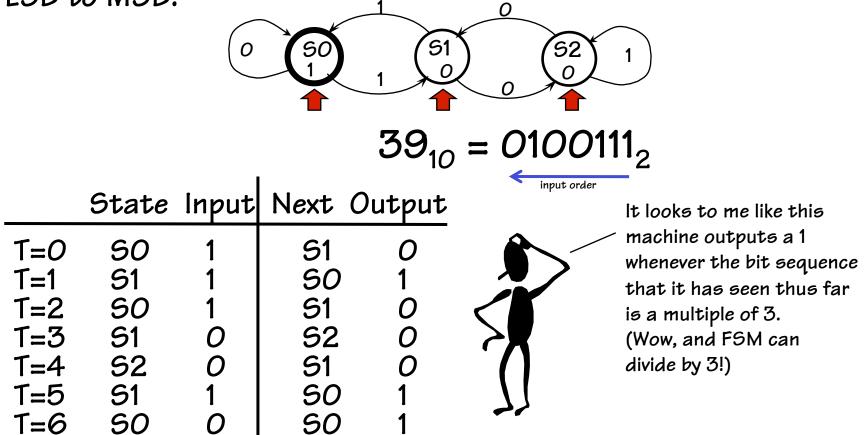

Let's emulate the behavior specified by the state machine shown below when processing the following string from LSB to MSB.

## FSM Party Games

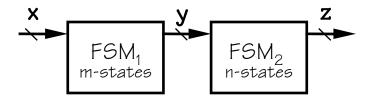

1. What can you say about the number of states?

States  $\leq 2^k$

2. Same question:

States  $\leq m \times n$

3. Here's an FSM. Can you discover its rules?

# What's My Transition Diagram?

- If you know NOTHING about the FSM, you're never sure!

- If you have a BOUND on the number of states, you can discover its behavior:

K-state FSM: Every (reachable) state can be reached in < 2<sup>i</sup> x k steps.

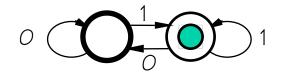

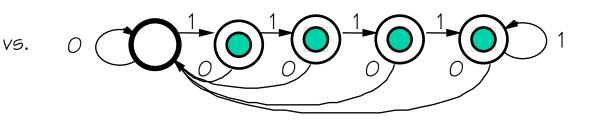

# FSM Equivalence

ARE THEY DIFFERENT?

NOT in any practical sense! They are EXTERNALLY INDISTINGUISHABLE, hence interchangeable.

FSMs are EQUIVALENT iff every input

sequence yields identical output sequences.

#### ENGINEERING GOAL:

- HAVE an FSM which works...

- WANT <u>simplest</u> (ergo cheapest) equivalent FSM.

# Housekeeping issues...

1. Initialization? Clear the memory?

- 2. Unused state encodings?

- waste ROM (use gates)

- meaning?

- 3. Synchronizing input changes with state update?

- 4. Choosing encoding for state?

# **2-Flavors of Processing Elements**

Combinational Logic: Table look-up, ROM

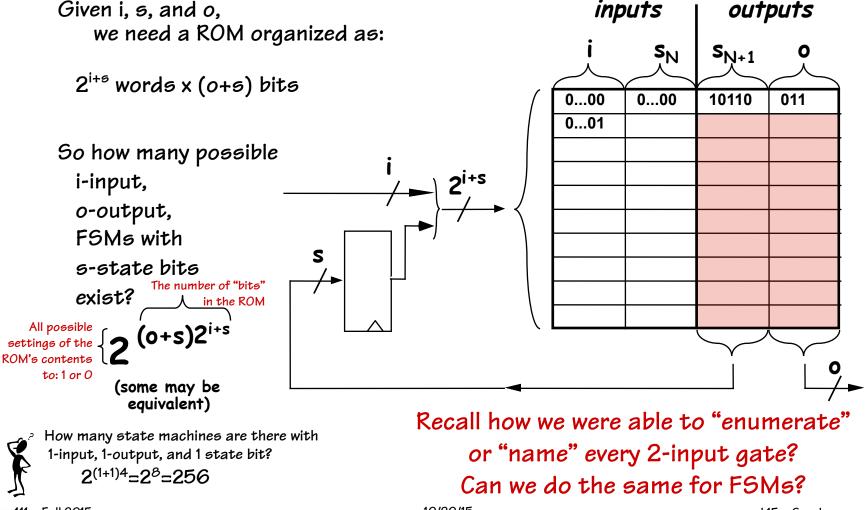

Recall that there are precisely

$2^{2^{i}}$ , i-input combinational functions. A single ROM can store 'o' of them.

Fundamentally, everything that we've learned so far can be done with a ROM and registers

F

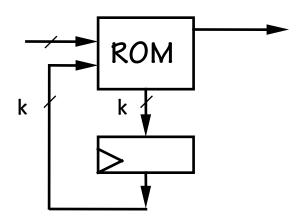

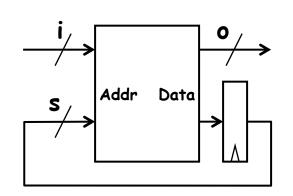

Finite State Machines: ROM with State Memory

Thus far, we know of nothing more powerful than an FSM

### FSMs as Programmable Machines

ROM-based FSM sketch:

An FSM's behavior is completely determined by its ROM contents.

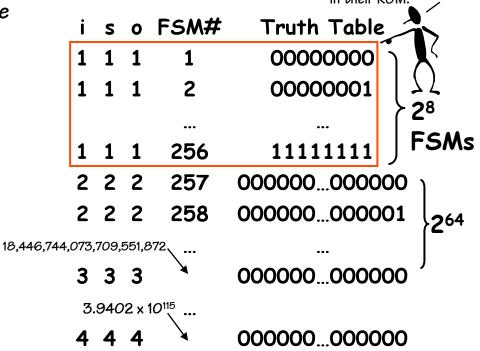

# **FSM** Enumeration

These are the FSMs with 1 input and 1 output and 1 state bit. They have 8-bits in their ROM.

### GOAL: List all possible FSMs in some canonical order.

- INFINITE list, but

- Every FSM has an entry in and an associated index.

| inp | outs | outputs |                  |  |

|-----|------|---------|------------------|--|

| i   | SN   | 0       | S <sub>N+1</sub> |  |

| 000 | 000  | 10110   | 011              |  |

| 001 |      |         |                  |  |

|     |      |         |                  |  |

|     |      |         |                  |  |

|     |      |         |                  |  |

|     |      |         |                  |  |

|     |      |         |                  |  |

|     |      |         |                  |  |

|     |      |         |                  |  |

| L   |      |         |                  |  |

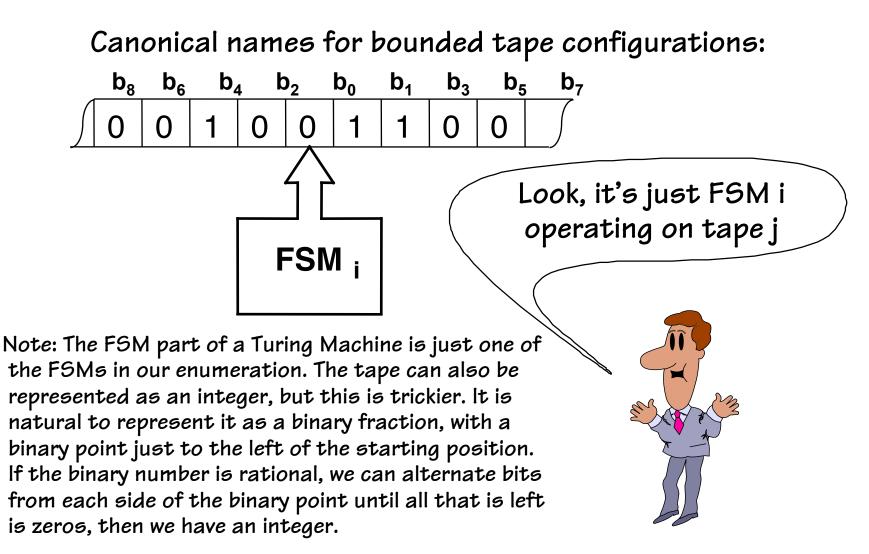

Every possible FSM can be associated with a unique number. This requires a few wasteful simplifications. First, given an i-input, s-state-bit, and o-output FSM, we'll replace it with its equivalent n-input, n-state-bit and n-output FSM, where n is the greatest of i, s, and o. We can always ignore the extra input-bits, and set the extra output bits to O. This allows us to discuss the i<sup>th</sup> FSM

## Some Perennial Favorites...

FSM<sub>837</sub> FSM<sub>1077</sub> FSM<sub>1537</sub> FSM<sub>89143</sub> FSM<sub>22698469884</sub> FSM<sub>784362783</sub> FSM<sub>784363783</sub> modulo 3 state machine 4-bit counter Combination lock Cheap digital watch Intel Pentium CPU – rev 1 Intel Pentium CPU – rev 2 Intel Pentium II CPU

## Can FSMs Compute Every Function?

### Nope!

There exist many simple problems that cannot be computed by FSMs. For instance:

### Checking for balanced parenthesis

(()(()())) - Okay (()())) - No good!

A function is specified by a deterministic output relationship for any given series of inputs, starting from a known initial state.

**PROBLEM:** Requires ARBITRARILY many states, depending on input. Must "COUNT" unmatched LEFT parens.

But, an FSM can only keep track of a "bounded" number of events. (Bounded by its number of states)

#### Is there a machine that can solve this problem?

## **Unbounded-Space** Computation

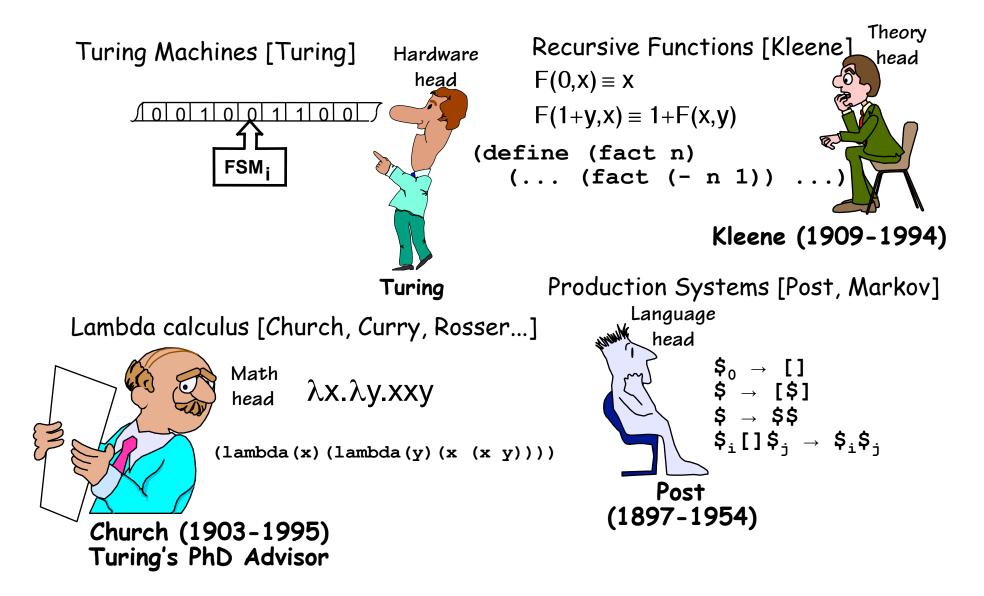

DURING 1920s & 1930s, much of the "science" part of computer science was being developed (long before actual electronic computers existed). Many different

#### "Models of Computation"

were proposed, and the classes of "functions" that each could compute were analyzed.

One of these models was the

#### "TURING MACHINE",

named after Alan Turing (1912-1954).

A Turing Machine is just an FSM which receives its inputs and writes outputs onto an "infinite tape". This simple addition overcomes the FSM's limitation that it can only keep track of a "bounded number of events".

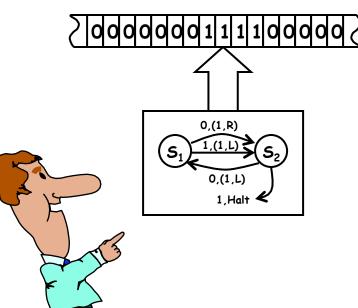

# A Turing Machine Example

#### **Turing Machine Specification**

- Infinite tape

- Discrete symbol positions

- Finite alphabet say {0, 1}

- Control FSM

INPUTS:

Current symbol on tape OUTPUTS:

write 0/1

- move Left/Right

- Initial Starting State {SO}

- Halt State {Halt}

A Turing machine, like an FSM, can be specified via a state-transition table. The following Turing Machine implements a unary (base 1) incrementer.

| Current    | Tape  | Write |      | Next       |

|------------|-------|-------|------|------------|

| State      | Input | Tape  | Move | State      |

| <b>S</b> 0 | 1     | 1     | R    | <b>S</b> 0 |

| <b>S</b> 0 | 0     | 1     | L    | <b>S</b> 1 |

| <b>S</b> 1 | 1     | 1     | L    | <b>S</b> 1 |

| <b>S</b> 1 | 0     | 0     | R    | Halt       |

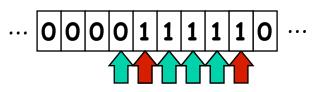

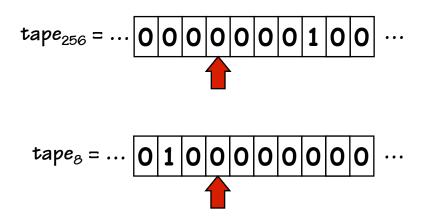

## Turing Machine Tapes as Integers

# TMs as Integer Functions

Turing Machine  $T_i$  operating on Tape x, where  $x = \dots b_8 b_7 b_6 b_5 b_4 b_3 b_2 b_1 b_0$

### Alternative Models of Computation

### The 1<sup>st</sup> Computer Industry Shakeout

## And the Battles Raged

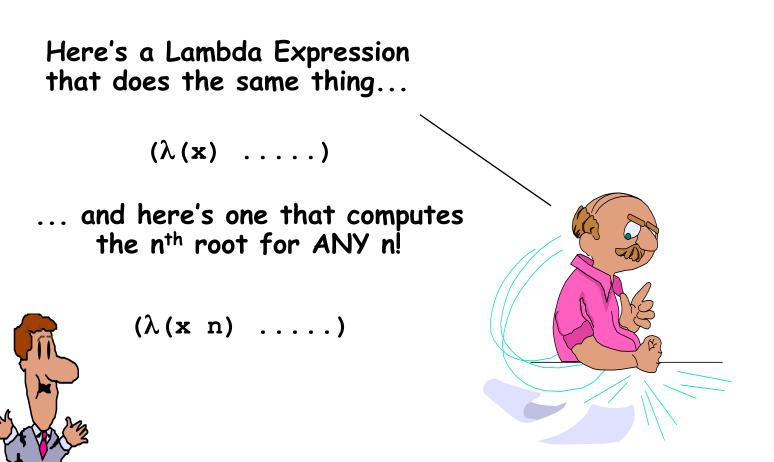

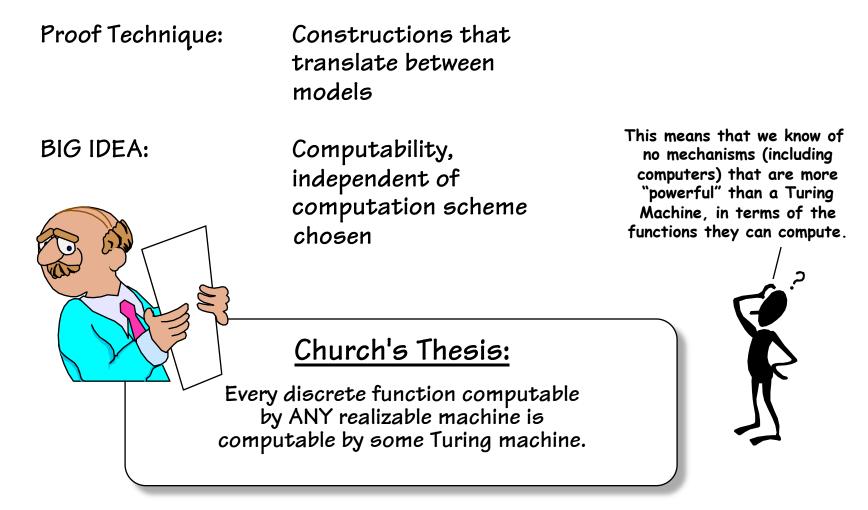

### Fundamental Result: Computable Functions

Each model is capable of computing <u>exactly</u> the same set of integer functions!

# **Computable Functions**

The "input" to our computable function will be given on the initial tape, and the "output" will be the contents of the tape when the TM halts.

$$f(x) computable <=> for some k, all x:$$

$$f(x) = T_{k}[x] \equiv f_{k}(x)$$

Representation tricks: to compute  $f_k(x,y)$  (2 inputs) <x,y> = integer whose even bits come from x, and whose odd bits come from y; whence

$$f_{K}(x, y) \equiv T_{K}[\langle x, y \rangle]$$

# TMs, like programs, can misbehave

It is possible that a given Turning Machine may not produce a result for a given input tape. And it may do so by entering an infinite loop!

Consider the given TM.

Its scans a tape looking for the first non-zero cell to the right.

What does it do when given a tape that has no 1's to its left?

We say this TM does not halt for that input!

| Current<br>State | • | Write<br>Tape | Move | Next<br>State |

|------------------|---|---------------|------|---------------|

| 50               | 1 | 1             | L    | Halt          |

| 50               | 0 | 0             | R    | S0            |

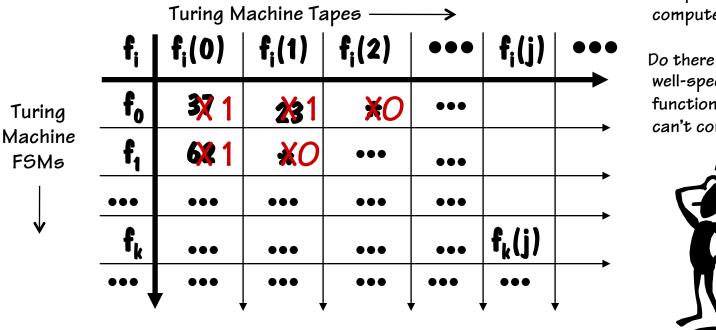

### **Enumeration of Computable functions**

#### Conceptual table of TM behaviors...

VERTICAL AXIS: Enumeration of TMs. HORIZONTAL AXIS: Enumeration of input tapes. (j, k) entry = result of  $TM_k[j]$  -- integer, or \* if never halts.

function is in this table, since everything that we know how to compute can be computed by a TM.

Every computable

Do there exist well-specified integer functions that a TM can't compute?

**The Halting Problem:** Given j, k: Does TM<sub>k</sub> Halt with input j?

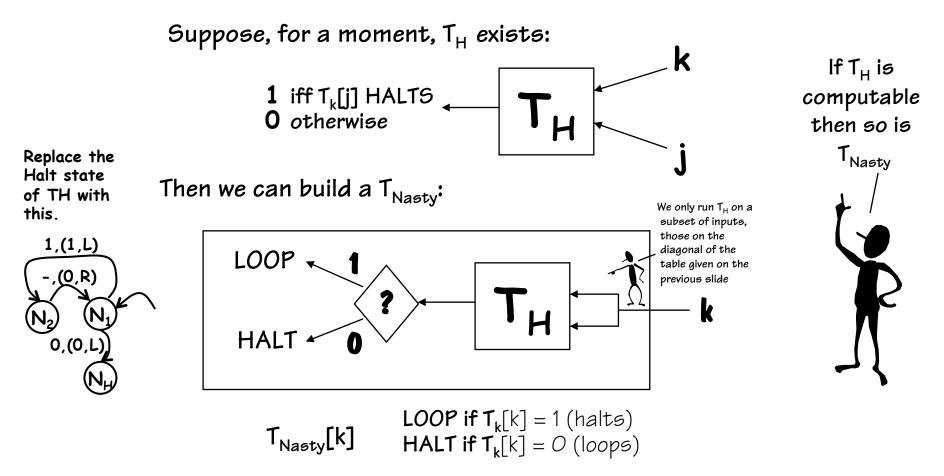

# The Halting Problem

**The Halting Function:**  $T_{H}[k, j] = 1$  iff  $TM_{k}[j]$  halts, else O

Can a Turing machine compute this function?

# What does T<sub>Nasty</sub>[Nasty] do?

Answer:

T<sub>Nasty</sub>[Nasty] loops if T<sub>Nasty</sub>[Nasty] halts T<sub>Nasty</sub>[Nasty] halts if T<sub>Nasty</sub>[Nasty] loops

That's a contradiction.

Thus, T<sub>H</sub> is uncomputable by a Turing Machine!

<u>Net Result</u>: There are some integer functions that Turing Machines simply cannot answer. Since, we know of no better model of computation than a Turing machine, this implies that there are some well-specified problems that defy computation.

### Reality: Limits of Turing Machines

A Turing machine is formal abstraction that addresses

- Fundamental Limits of Computability What is means to compute. The existence of incomputable functions.

- We know of no machine more powerful than a Turing machine in terms of the functions that it can compute.

But they ignore

- Practical coding of programs

- Performance

- Implementability

- Programmability

- ... these latter issues are the primary focus of contemporary computer science (Remainder of Comp 411)

# Computability vs. Programmability

#### Recall Church's thesis:

00000001111100000 0,(1,R) (S1 1,(1,L) (S2 0,(1,L) 1,Halt

Alan Turing

"Any discrete function computable by ANY realizable machine is computable by some Turing Machine"

Thus, we've defined what it means to COMPUTE (whatever a TM can compute)

- A Turing machine is nothing more that an FSM that receives inputs from, and outputs onto, an infinite tape.

- Thus far, we've been designing a new Turing machine FSM for each new function that we encounter.

Wouldn't it be nice if we could design a more general purpose computing machine?

# Too many Turing machines!

## Programs as Data

What if we encoded the description of the FSM on our tape, and then wrote a general purpose FSM to read the tape and EMULATE the behavior of the encoded machine? We could just store the state-transition table for our TM on the tape and then design a new TM that makes reference to it as often as it likes. It seems possible that such a machine could be built.

"It is possible to invent a single machine which can be used to compute any computable sequence. If this machine U is supplied with a tape on the beginning of which is written the S.D ["standard description" of an action table] of some computing machine M, then U will compute the same sequence as M." - Turing 1936 (Proc of the London Mathematical Society, Ser. 2, Vol. 42)

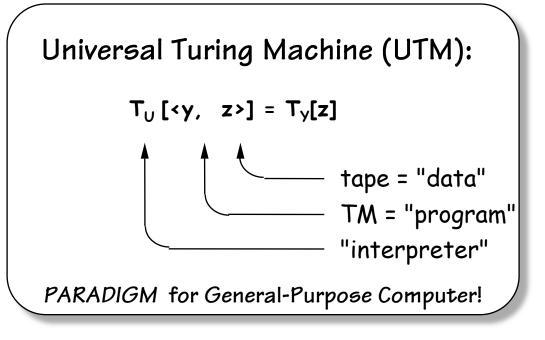

# Fundamental Result: Universality

Define "Universal Function":  $U(x,y) = T_{\chi}(y)$  for every x, y ... Surprise! U(x,y) IS COMPUTABLE,

hence  $U(x,y) = T_U(\langle x,y \rangle)$  for some U.

INFINITELY many UTMs ... Any one of them can evaluate any computable function by simulating/ emulating/interpreting the actions of Turing machine given to it as an input.

#### UNIVERSALITY:

Basic requirement for a general purpose computer

# **Demonstrating Universality**

Suppose you've designed Turing Machine  $T_k$  and want to show that its universal.

APPROACH:

- 1. Find some known universal machine, say  $T_U$ .

- 2. Devise a program, P, to simulate  $T_U$  on  $T_K$ :  $T_K[<P,x>] = T_U[x]$  for all x.

- 3. Since  $T_U[\langle y, z \rangle] = T_Y[z]$ , it follows that, for all y and z.

$$T_{K} [\langle P, \langle y, z \rangle \rangle] = T_{U} [\langle y, z \rangle] = T_{y} [z]$$

**CONCLUSION:** Armed with program **P**, machine  $T_K$  can mimic the behavior of an arbitrary machine  $T_Y$  operating on an arbitrary input tape z.

HENCE T<sub>k</sub> can compute any function that can be computed by any Turing Machine. Turing Complete

### Interpretive Layers: What's going on?

$$T_{K} [\langle P, \langle y, z \rangle \rangle] = T_{U} [\langle y, z \rangle] = T_{y} [z]$$

#### Multiple levels of interpretation:

| T <sub>y</sub> [z]                      | Application (Desired user function) |

|-----------------------------------------|-------------------------------------|

| T <sub>U</sub> [ <y,z>]</y,z>           | Portable Language / Virtual Machine |

| T <sub>K</sub> [ <p,<y,z>&gt;]</p,<y,z> | Computing Hardware / Bare Metal     |

#### Benefits of Interpretation:

**BOOTSTRAP** high-level functionality on very simple hardware.

Deal with "IDEAL" machines rather than real machines.

**REAL MACHINES** are built this way - several interpretive layers.

# Power of Interpretation

BIG IDEA: Manipulate *coded representations* of computing machines, rather than the machines themselves.

- PROGRAM as a behavioral description

- SOFTWARE vs. HARDWARE

- INTERPRETER as machine which takes program and mimics behavior it describes

- LANGUAGE as interface between interpreter and program

- COMPILER as translator between languages:

INTELLECTUAL BENEFITS:

- Programs as data -- mathematical objects

- Combination, composition, generation, parameterization, etc.