### ARITHMETIC CIRCUITS

# REVIEW: BINARY REPRESENTATIONS

- Unsigned numbers, each increasingly significant bit has a weight of the next larger power of 2

- Signed 2's complement representation the most significant bit is a negative power of 2.

unsigned:

$$v = \sum_{i=0}^{n-1} 2^i b_i$$

signed:  $v = -2^{n-1} b_{n-1} + \sum_{i=0}^{n-2} 2^i b_i$

• Why?

They are compatible. The same logic can be used for both

Only "adders" are needed for both addition and subtraction

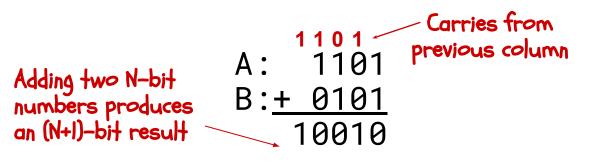

### BINARY ADDITION

В

coFA ci

Here's an example of binary addition as one might do it by "hand":

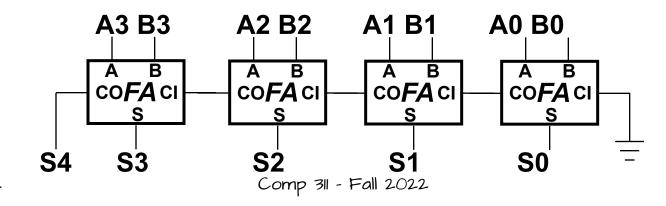

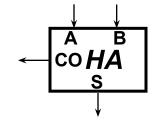

Let's start by building a block to add one column: « This functional block is called a "Full-adder"

Then we can cascade them to add two numbers of any size ...

## DESIGN OF A "FULL ADDER"

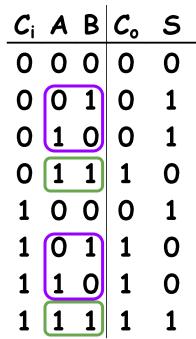

1) Start with a truth table:

2) Write down equations for the "1" outputs

3) Simplifying a bit CO = (CI & (A | B)) | (A & B) S = CI ^ A ^ B

| Ci     |             |        | C <sub>o</sub> | S |

|--------|-------------|--------|----------------|---|

| 0<br>0 | 0           | 0<br>1 | 0              | 0 |

| 0      | 0           | 1      | 0              | 1 |

| 0      | 1           | 0      | 0              | 1 |

| 0      | 1<br>0<br>0 | 1      | 1              | 0 |

| 1      | 0           | 0      | 0              | 1 |

| 1      | 0           | 1      | 1              | 0 |

| 1      | 1           | 0      | 1              | 0 |

| 1      | 1           | 1      | 1              | 1 |

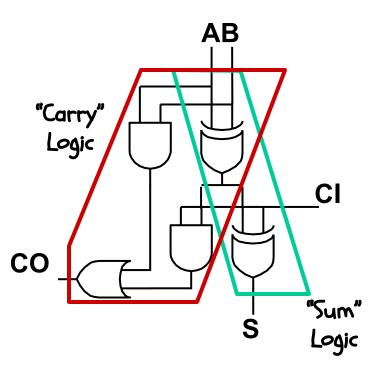

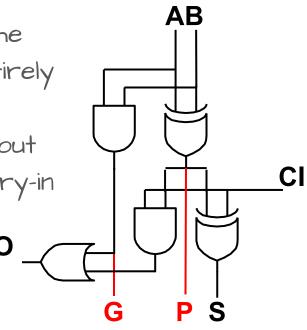

### AS A LOGIC DIAGRAM

- Our equations:

CO = (CI & (A ^ B)) | (A & B)

S = CI ^ (A ^ B)

- A little tricky, but finally Only 5 gates/bit

### AN ASIDE: WHY FULL ADDER?

Suppose you don't want/need a carry-in?

Then you get a "half adder" with 2 inputs and 2 outputs:

AB

| A | В | СО | 5 |

|---|---|----|---|

| 0 | 0 | 0  | 0 |

| 0 | 1 | 0  | 1 |

| 1 | 0 | 0  | 1 |

| 1 | 1 | 1  | 0 |

Half-adder equations:

CO = A & B

S = A ^ B

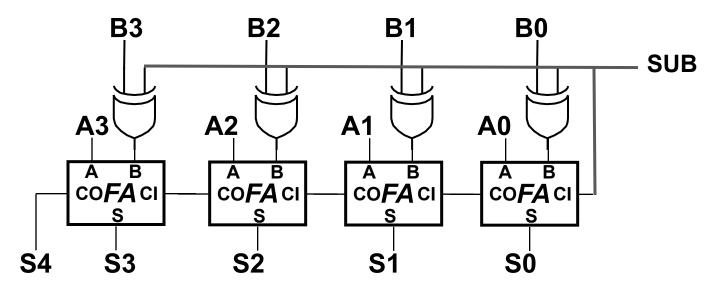

SUBTRACTION: A - B = A + (-B)

- Recall the trick was to "complement and add I"

- How to complement?

~ = bitwise complement

Β

B

• So now a unit that can either add or subtract

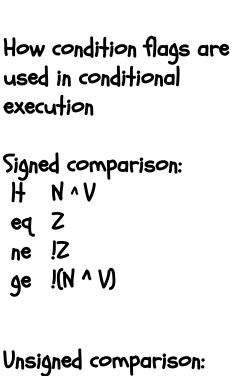

### CONDITION FLAGS

Besides the sum, one often wants four other bits of information from an arithmetic unit, the condition flags.

Z (zero): result is = 0 big NOR gate N (negative): result is < 0 53 C (carry): indicates the most significant bit produced a carry, e.g., "I + (-I)"

CO3 (of last FA)

V (overflow): indicates an unexpected change in sign e.q.,  $(2^{30} - 1) + 1''$  (,  $(A_{2} \& B_{3} \& S_{3}) | (A_{3} \& B_{3} \& S_{3})$

Hu!C (same as cc) geu C (same as cs)

Comp 311 - Fall 2022

-- or --

$CO_{31} \cap CO_{30}$

10/5/2022

$\mathbf{t}_{\text{PD}} = (\mathbf{t}_{\text{PD,XOR}} + \mathbf{t}_{\text{PD,AND}} + \mathbf{t}_{\text{PD,OR}}) + (N-2)^* (\mathbf{t}_{\text{PD,OR}} + \mathbf{t}_{\text{PD,AND}}) + \mathbf{t}_{\text{PD,XOR}} \approx \Theta(N)$

### 9

-CI

A B

### HOW FAST IS AN ADD?

$\mathbf{A}_{n-1}\mathbf{B}_{n-1}$  $A_{12} B_{12}$ B<sub>10</sub>  $\mathbf{A}_{|n-2|}\mathbf{B}_{n-2}$ B<sub>1</sub> Â В A B CO**FA** CI B co**FAC** COFA CI COFA CI COFA CI S S **S**<sub>30</sub> S, Worse-case path: carry propagation from LSB to MSB, e.g., when adding -1 to 1.

Determined by  $T_{pd}$  of the FA chain

### WE CAN ADD "MUCH" FASTER

- P, Propagate, means the carry-out depends entirely on the carry-in

- G, generates a carry-out regardless of the carry-in

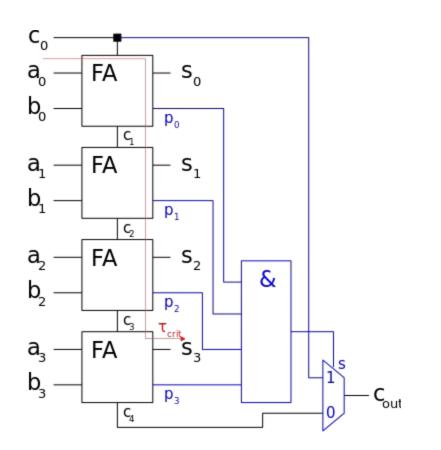

### CARRY-SKIP ADDERS

If all full adders in a contiguous block have their Propagate true, then the incoming carry-in can "skip" over the entire block!

Requires extra AND gates and a MUX, but reduces the worst case add-time

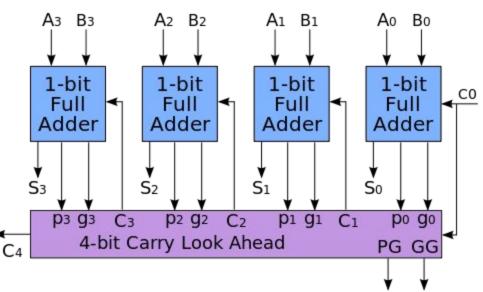

FULL CARRY-LOOKAHEAD

The fastest adders use full carry look-ahead.

Given the Ps and Gs

of a block, one can

simultaneously

compute the

carry-ins for all

bits as well as

the block using

the 3-level SOP

methods discussed last

methods discussed last lecture.

Results in an ⊖(log<sub>2</sub>(N)), T<sub>pd</sub>, like an N-input AND gate, using ≈2x more gates

### NEXT TIME

### We get shifty, no, Bool!