## ADDRESSING MODES AND BRANCHES

- More on Immediates

- Reading and Writing Memory

- Registers holding addresses

- Pointers

- Changing the PC

- Loops

- Labels

- Calling Functions

#### WHY BUILT-IN CONSTANT OPERANDS? (IMMEDIATES)

|         | 31 30 29 28 27 26 25 24 23 22 21 20 | 19 18 17 16 15 | 14 13 12 11 10 9 | 876 | 5 4 3 2 1 0 |

|---------|-------------------------------------|----------------|------------------|-----|-------------|

| I-type: | imm12                               | rs1            | func3 rd         | 0   | 0 1 0 0 1 1 |

- Alternatives? Why not? Do we have a choice?

put constants in memory (was common in older ISAs)

- SMALL constants are used frequently (50% of operands)

In a C compiler (gcc) 52% of ALU operations involve a constant

In a circuit simulator (spice) 69% involve constants

e.g., B = B + 1; C = W & Oxff; A = B 1;

- ISA Design Principle: Make the common case easy Make the common case fast

How large of constants should we allow for? If they are too big, we won't have enough bits leftover for the instructions or operands.

## BIGGER CONSTANTS

We can load any 32-bit constant using a series of instructions

| addi | x10,x0,0x123  |                       |

|------|---------------|-----------------------|

| slli | x10,x10,12    | Five instructions, is |

| addi | x10,x10,0x456 | there a better way?   |

| slli | x10,x10,12    | V                     |

| addi | x10,x10,0x78  |                       |

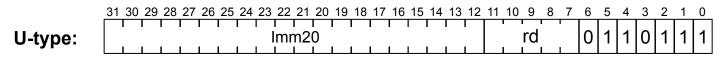

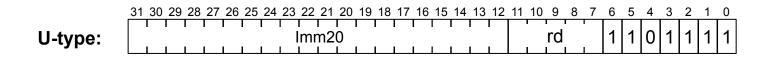

But there there is a special instruction for constructing large constants., called "Load Upper Immediate" or **lui**. lui uses a new instruction format call the U-type. lui can be used as part of a two-instruction sequence to construct any 32-bit constant

**luix10**,0x12345 # encoded as 0x12345537

# LOAD AND STORE INSTRUCTIONS

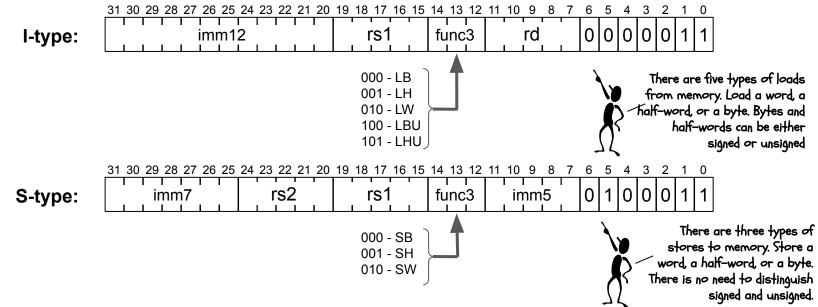

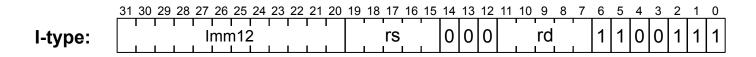

RISC-V is a "Load/Store architecture". That means that only a specific class of instructions are used to reference data in memory. As a rule, data is loaded into registers first, then processed, and the results are written back using stores. Load and Store instructions have their own format:

Comp 311 - Fall 2022

## LOAD AND STORE OPTIONS

RISC-V's load and store instructions are versatile. They provide a wide range of addressing modes. Only a subset is shown here.

$\label{eq:Rd} \begin{array}{c} \mathsf{Rd} \leftarrow \mathsf{Memory}[\mathsf{Rs} + \mathsf{imm12}] \\ \mathsf{Rd} \text{ is loaded with the contents of memory at the address found by} \\ \mathsf{adding the contents of the base register, } \mathsf{Rs, to the supplied} \end{array}$ constant

## CHANGING THE PC

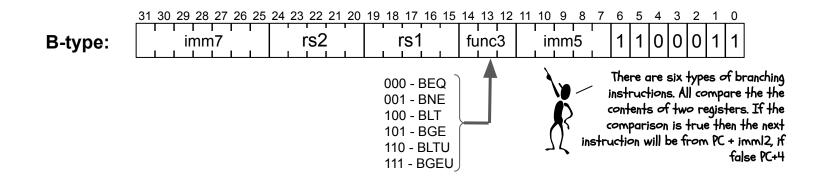

The Program Counter, or PC, is a special register that points to the address of the next instruction to be fetched. There are special instructions for changing the PC. One type is Branching Instructions. Branches are to nearby place within +/- 512 instructions away.

### BRANCH EXAMPLES

bne x10, x0, else if the contents of x10 is not equal to 0 then branch to the nearby address with the label "else" blt x10, x0, neg

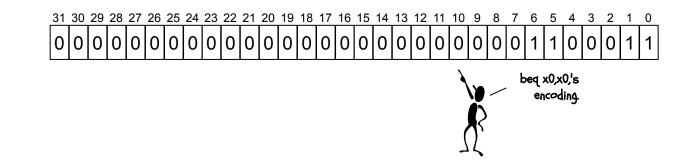

loop: beq

$$x0, x0, loop$$

An infinite loop.

## PC RELATIVE OFFSETS

All branch offsets in RISC-V are added to the PC to determine the target address of the next instruction in the case of a valid condition. Earlier ISAs would instead specify the "absolute" target address. What are the advantages of "relative" vs "absolute"?

- Does not implicitly limit the address space

- Requires fewer instruction bits, supports the most common cases

- Allows for "relocatable" code

### A SIMPLE PROGRAM

```

Assembly code for

#

#

sum = 0;

# for (i = 0; i <= 10; i++)

#

sum = sum + i;

addi x7,x0,11

# x7 is 10 + 1

addi x5,x0,0

# x5 is i

addi x6,x0,0

# x6 is sum

loop:

add x6,x6,x5

# sum = sum + i

addi x5,x5,1

# i++

blt

x5, x7, loop

halt:

beq

x0,x0,halt

```

## MEET THE MINIRISCV SIMULATOR

Located at:

https://csbio.unc.edu/mcmillan/miniRISCV.html

Or click the link in the "RESOURCES" section of the course website

UNC miniRISC-V Architecture Simulator V 0.1

| # Asse | embly co | de for         |           |       |             |            |    |          |     |

|--------|----------|----------------|-----------|-------|-------------|------------|----|----------|-----|

| # sum  | = 0;     |                |           |       |             |            |    |          |     |

|        |          | i <= 10; i++   | -)        |       |             |            |    |          |     |

| #      | sum = si |                |           |       |             |            |    |          |     |

|        | addi     | x7,x0,11       | # x7 is   | 10 +  | 1           |            |    |          |     |

|        | addi     | x5,x0,0        | # x5 is   | i     |             |            |    |          |     |

|        | addi     | x6,x0,0        | # x6 is   | sum   |             |            |    |          |     |

| loop:  | add      | x6,x6,x5       | # sum =   | sum + | i           |            |    |          |     |

|        | addi     | x5,x5,1        | # i++     |       |             |            |    |          |     |

|        |          | x5,x7,loop     |           |       |             |            |    |          |     |

| halt:  | beq      | x0,x0,halt     |           |       |             |            |    |          |     |

|        |          |                |           |       |             |            |    |          |     |

|        |          |                |           |       |             |            |    |          |     |

|        |          |                |           |       |             |            |    |          |     |

|        |          |                |           |       |             |            |    |          |     |

|        |          |                |           |       |             |            |    |          |     |

|        |          |                |           |       |             |            |    |          |     |

|        |          |                |           |       |             |            |    |          |     |

|        |          |                |           |       |             |            |    |          |     |

|        |          |                |           |       |             |            |    |          |     |

|        |          |                |           |       |             |            |    |          |     |

|        |          |                |           |       |             |            |    |          |     |

|        |          |                |           |       |             |            |    |          |     |

|        |          |                |           |       |             |            |    |          |     |

|        |          |                |           |       |             |            |    |          |     |

|        |          |                |           |       |             |            |    |          |     |

|        |          |                |           |       |             |            |    |          |     |

|        |          |                |           |       |             |            |    |          |     |

|        |          |                |           |       |             |            |    |          |     |

|        |          |                |           |       |             |            |    |          |     |

| Assemb | le Reset | Step Multistep | 10        | Run   | Memory Dump | 0x00000000 | A  | dvanced  | ~   |

|        |          |                | Registers |       |             |            | pc | : [0x000 | 000 |

|        |          |                |           |       | -           |            |    |          | -   |

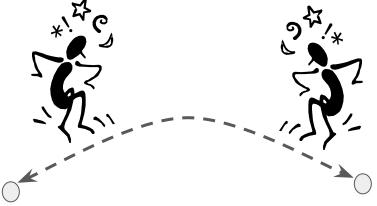

#### JUMPING LONG DISTANCES

There are two more instructions for jumping long distances. Both are "unconditional", meaning that the branch is always taken, but they have another interesting feature

#### **JAL**: jump and link

Syntax: jal rd,imm20 jair can be used to jump to an absolute location by first loading the address into a register

Description:

$Reg[d] \leftarrow PC + 4$  $PC \leftarrow PC + sign extended(imm20)$

Write the address of the following instruction, PC + 4, into Reg[d], then jump to the instruction that is found by adding the current PC to the signed immediate offset. In practice this is usually specified by a label.

There are two more instructions for jumping long distances. Both are "unconditional", meaning that the branch is always taken, but they have another interesting feature

**JALR**: jump and link register

Syntax: jalr rd,imm12(rs) jalr rd,(rs)

Description:

$Reg[d] \leftarrow PC + 4$  $PC \leftarrow Reg[s] + sign\_extended(imm12)$

Jump to the instruction given by the contents of *Reg[s]*, and save the location of the next instruction in *Reg[s]*.

## WHY STORE PC + 4?

These long-distance "jump" instructions also save the address of the following instruction in a register specified by **Rd**. Often, this register will be xO, and therefore is ignored. But in other cases it is useful to get back to where we jumped from. More about this next lecture.

#### Still some loose ends

NEXT TIME

Multiplication? Division? Floating point? Relocatable data

We'll write more Assembly programs